# Laboratory 6

(Due date: **011**: December 3<sup>rd</sup>, **005**: December 4<sup>th</sup>, **007**: December 5<sup>th</sup>)

## **OBJECTIVES**

- ✓ Describe Finite State Machines (FSMs) in VHDL.

- ✓ Implement a Digital System: Control Unit and Datapath Unit.

#### VHDL CODING

✓ Refer to the Tutorial: VHDL for FPGAs for parametric code for: register, shift register, counter, adder/subtractor.

## ITERATIVE SQUARE ROOT IMPLEMENTATION (100/100)

• Given an unsigned integer D, we want to design a circuit that computes the square root Q and remainder R ( $R = D - Q \times Q$ ). There exist many algorithms for hardware implementation, and the following one has proved to outperform most others:

$$\begin{aligned} & \text{Radical } (2n \text{ bits}) \colon & D = d_{2n-1}d_{2n-2}d_{2n-3}d_{2n-4} \dots d_1d_0 \\ & \text{We define:} & Q_k = q_{n-1}q_{n-2} \dots q_k, & k = 0,1,\dots,n-1 \\ & R'_k = r'_n r'_{n-1} r'_{n-2} \dots r'_k, & k = 0,1,\dots,n-1 \end{aligned}$$

$$\begin{aligned} & \text{for } k = n-1 \to 0 \\ & \text{if } k = n-1 \text{ then} \\ & R'_k = d_{2k+1}d_{2k} - 01 & (R'_{n-1} = d_{2n-1}d_{2n-2} - 01) \\ & \text{else} \end{aligned}$$

$$R'_k = \begin{cases} R'_{k+1}d_{2k+1}d_{2k} - Q_{k+1}01, & \text{if } q_{k+1} = 1 \\ R'_{k+1}d_{2k+1}d_{2k+1}d_{2k} + Q_{k+1}11, & \text{if } q_{k+1} = 0 \end{cases}$$

$$end$$

$$q_k = \begin{cases} 1, \text{if } R'_k \geq 0 \\ 0, \text{if } R'_k < 0 \end{cases}$$

Square Root (n bits):  $Q = q_{n-1}q_{n-2} \dots q_0$   $Q_k$ : unsigned integer with n-k bits.  $R'_k$ : signed (2C) integer with n-k+1 bits.

- Q and  $R'_{n-1}$  are initialized with 0's.

- This is a non-restoring algorithm, meaning that at the last iteration we might not have the correct remainder R. To get the correct value of R, an extra operation would be required.

Remainder:

$$R = R_0 = \begin{cases} R'_0, & \text{if } R'_0 \ge 0 \\ R'_0 + Q_0 1, & \text{if } R'_0 < 0 \end{cases}$$

In practice, the remainder R is rarely used, and we do not implement that extra operation here.

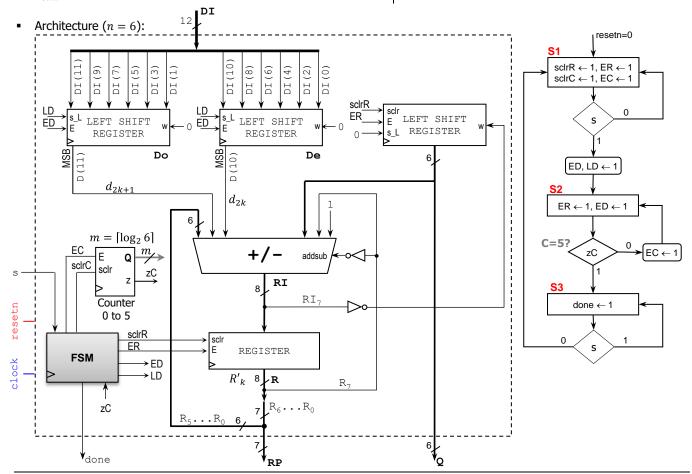

- Based on the algorithm, an iterative architecture for n=6 is presented. The register  $\mathbf{R}$  stores the 'estimated remainder'  $R'_k$  at each iteration. A square root operation is started when s=1 (where the 12-bit input  $\mathtt{DI}$  is captured). The signal done is asserted to indicate that the operation has been completed and the result appears in register  $\mathbf{Q}$  (and  $R'_0$  appears in  $\mathbf{RP}$ )

- $\checkmark$  At each iteration,  $q_k$  (a bit of the square root Q) is computed and shifted into the register Q.

- ✓ The input data DI is captured into shift register D. The bits  $d_{2k+1}d_{2k}$  correspond to the 2 MSBs of the register D. At every iteration, the register D shifts two bits to the left.

- Register D: implemented by two parallel access shift registers: Do (for odd bits of D) and De (for even bits of D).

- $\checkmark$  Note that on RP, we get  $R'_0$  at the end of the computations. This is a 7-bit signed number. If it is positive, it is the correct remainder. If it is negative, an extra operation is required to get the correct remainder (not implemented in this circuit).

- $\checkmark$  On register Q, we get the result, which is the square root Q, a 6-bit unsigned integer.

- The circuit includes three 6-bit parallel access left shift registers, an 8-bit register, a modulo-6 counter, an 8-bit adder/subtractor (addsub=0: add, addsub=1: subtract), and an FSM. Each sequential component has resetn and clock inputs.

- The circuit is an example of a Digital System: It includes a Control Circuit (FSM) and a Datapath Circuit. The Datapath Circuit is made from combinational and sequential components. The circuit is also called a Special-Purpose Processor. In this case, the special purpose is the integer square root.

### **PROCEDURE**

## Vivado: Complete the following steps:

- Create a new Vivado Project. Select the corresponding Artix-7 FPGA device (e.g.: the XC7A50T-1CSG324 FPGA device for the Nexys A7-50T).

- ✓ Write the VHDL code for the given circuit. <u>Synthesize</u> your circuit to clear syntax errors.

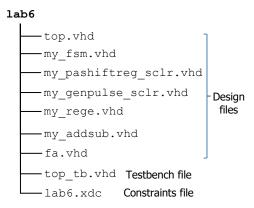

- Use the Structural Description: Have a separate file for the counter, parallel access shift register with sclr, register, adder/subtractor, FSM, and top file.

- Suggestion: Use parametric code (set up the proper parameters with generic map) for these components:

- · Parallel access shift registers with sclr: my\_pashiftreg\_sclr

- \* Note that some of these shift registers do not use the sclr input. In this case, that input should be tied to '0'.

- Counter: my\_genpulse\_sclr (include in the top file: use ieee.math\_real.log2; use ieee.math\_real.ceil;)

- Register with enable: my\_rege

- · Adder/subtractor: my\_addsub

- ✓ Write the VHDL testbench (generate a 100 MHz input clock for your simulations) to test the following cases:

| DI                  | Q           | RP             | Comments                                               |

|---------------------|-------------|----------------|--------------------------------------------------------|

| 101010101010 (2730) | 110100 (52) | 0110001 (0x31) | Remainder <b>✓</b>                                     |

| 001001101111 (623)  | 011000 (24) | 1111110 (0x7E) | Correct remainder:<br>1111110+0110001 = AF = <b>2F</b> |

| 111110000010 (3970) | 111111 (63) | 0000001 (0x01) | Remainder <b>✓</b>                                     |

| 000100100001 (289)  | 010001 (17) | 0000000 (0x00) | Remainder <b>✓</b>                                     |

| 010110111110 (1470) | 100110 (38) | 1001101 (0x4D) | Correct remainder:<br>1001101+1001101 = 9A = <b>1A</b> |

| 100010100001 (2209) | 101111 (47) | 0000000 (0x00) | Remainder <b>✓</b>                                     |

- Note that RP is a 7-bit signed number. If it is positive, RP has the correct remainder. If it is negative, the correct remainder is an unsigned 7-bit number, that can be obtained by taking the 7 LSBs out of the operation  $R'_0 + Q_0 1$ .

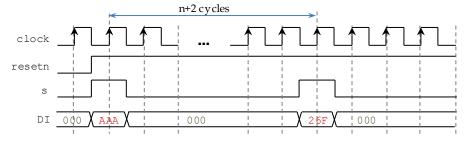

- The testbench should be written according to the timing diagram shown in the figure, where the first two values for DI are fed. Note that there are n + 2 = 8 cycles between data values.

- ✓ Perform <u>Behavioral Simulation</u> and <u>Timing Simulation</u> of your design. **Demonstrate this to your TA**.

- Behavioral Simulation: To help debug your circuit, add the internal signals (state, Do, De, RI) to the waveform view. Go to: SCOPE window: testbench → UUT. Then go to Objects Window → Signal(s) → Add to Wave Window. Then, re-run the simulation.

- Note that you can represent data as unsigned integers (use Radix → Unsigned Decimal).

- If your circuit works as expected, the result appears on Q and RP when done=1. Verify that the values of Q and RP (when done=1) match those listed in the previous table.

- ✓ I/O Assignment: Create the XDC file associated with your board.

- Suggestion (for Basys 3, use SW15 instead of CPU RESETN for resetn input)

| Board pin names      | CLK100MHZ | CPU_RESETN | SW15 | SW11-SW0                          | LED15 | LED12-LED6                       | LED5-LED0                      |

|----------------------|-----------|------------|------|-----------------------------------|-------|----------------------------------|--------------------------------|

| Signal names in code | clock     | resetn     | s    | DI <sub>11</sub> -DI <sub>0</sub> | done  | RP <sub>6</sub> -RP <sub>0</sub> | Q <sub>5</sub> -Q <sub>0</sub> |

- The board pin names (except CPU\_RESETN) are used by all the listed boards (Nexys A7-50T/A7-100T, Nexys 4/DDR, Basys 3). I/Os: all switches and LEDs are active-high.

- Note: synchronous circuits always require a clock and reset signal.

- ✓ Reset signal: As a convention in this class, we use active-low reset (resetn). As a result, ensure that resetn is tied to the proper board resource:

- · Nexys A7-50T/A7-100T, Nexys 4/DDR: For resetn, use CPU RESETN pin. This is an active-low push button.

- Basys 3: There is no active low push button. Thus, for *resetn*, use SW15. Even though SW15 is active high, we can still think of it as active-low *resetn*, where the circuit is reset when the switch position is OFF ('0').

- ✓ Clock signal: Like other signals in the XDC file, you need to uncomment the lines associated with the clock signal and replace the signal label with name used in your code. In addition, there is parameter -period that is set by default to 10.00. This is the period (in ns) that your circuit should support.

- Basis 3: In these lines, replace the label clk with the signal name used in your code (clock): set\_property PACKAGE\_PIN W5 [get\_ports clk] set\_property IOSTANDARD LVCMOS33 [get\_ports clk] create\_clock -add -name sys\_clk\_pin -period 10.00 -waveform {0 5} [get\_ports clk]

- ✓ Generate and download the bitstream on the FPGA. Test the circuit (use the same input values as in the testbench). **Demonstrate this to your TA**.

## **SUBMISSION**

- Submit to Moodle (an assignment will be created):

- ✓ This lab sheet (as a .pdf) completed and signed off by the TA (or instructor)

- (<u>As a .zip file</u>) all the generated files: VHDL code files, VHDL testbench, and XDC file. **DO NOT submit the whole Vivado Project**.

- Your .zip file should only include one folder (the figure shows and example). Do not include subdirectories.

- It is strongly recommended that all your design files, testbench, and constraints file be located in a single directory. This will allow for a smooth experience with Vivado.

- You should only submit your source files AFTER you have demoed your work. Submission of work files without demoing will be assigned NO CREDIT.

| TA signature: | Date: |  |

|---------------|-------|--|

|               |       |  |